본 내용은 Yuan Taur and Tak H.Ning의 <Fundamentals of Modern VLSI Devices>를 참고하여 제작되었다.

일단 기본적으로 두 개의 구별되고 안정된 상태로 programmed 될 수 있다면 SRAM cell 의 storage element로써 사용될 수 있다. 거기다가 SRAM을 만들기 위해서는 하나 또는 그 이상의 access transistor가 필요하다. 이번 섹션에서는 CMOS SRAM cell들의 기본 작동원리, 디자인과 스케일링 이슈에 대해 다루고, bipolar SRAM cell의 기본적인 작동 원리에 대해 알아보려고 한다.

1. CMOS SRAM Cell

CMOS VLSI design에서 가장 많이 쓰이는 SRAM storage element는 CMOS inverter가 교차 결합된 형태는 bistable latch이다. 그림을 참고하자.

이러한 element로부터 transfer curve를 그리면, 다음과 같이 나온다. 이를 butterfly plot이라고 부른다.

인버터1 입력이 high면, 인버터1 출력이 low , 인버터2 입력에 low가 들어가고, 인버터1 입력이 low면, 인버터1 출력이 high, 인버터2 입력이 high가 들어가므로 두 가지 안정된 상태가 저장될 수 있다. bistable latch구조는 저장된 상태를 바꾸기 위한 외부 신호가 들어오지 않는한 한 가지의 상태로 유지된다.

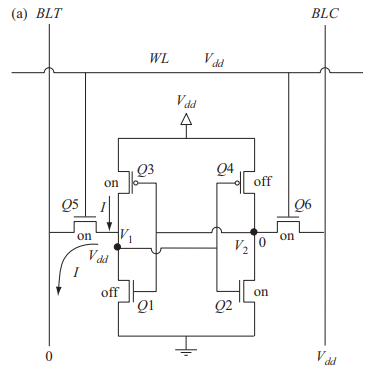

가장 보편적으로 쓰는 SRAM cell은 6개의 transistor cell, 2개의 인버터와 2개의 access transistors으로 구성된다. circuit schematic은 다음과 같다.

두 개의 인버터들은 n-channel access transistors인 Q5, Q6를 통해 두 개의 bitline, BLT(bitline true)과 BLC(bitline complement)와 연결되어 있다. access transistor들은 wordline(WL) voltage를 통해 컨트롤 될 수 있다. standby 모드에서는 WL를 low로 유지시키고 그렇게 되면 access transistor들이 꺼져 bitline과 cross-coupled inverter이 분리가 되게 된다.

1.1 CMOS SRAM Cell의 기본 동작

1) Read 동작

Read state '0' (standby value : V(BLT) = V(BLC) = V1 =Vdd, V2 = 0 인 상태)

① 두 bitline들을 Vdd로 precharge시킨다. 단, 낮은 임피던스의 Z로 연결되어 있다.

② WL : High(selected) -> access transistor : ON

③ charge가 BLC에서 V2로 흐르면서, V2는 증가하고, V(BLC)는 감소한다.

④ bitline voltage difference, V(BLT)-V(BLC)>0 인 값이 두 bitline들과 연결되어 있는 sense amplifier로 읽혀진다.(Read)

⑤ WL : Low -> access transistor : OFF

Read state '1' (standby value : V(BLT) = V(BLC) = V2 =Vdd, V1 = 0 인 상태)

① 두 bitline들을 Vdd로 precharge시킨다. 단, 낮은 임피던스의 Z로 연결되어 있다.

② WL : High(selected) -> access transistor : ON

③ charge가 BLT에서 V1로 흐르면서, V1는 증가하고, V(BLT)는 감소한다.

④ bitline voltage difference, V(BLT)-V(BLC)<0 인 값이 두 bitline들과 연결되어 있는 sense amplifier로 읽혀진다.(Read)

⑤ WL : Low -> access transistor : OFF

access transistor가 OFF가 되면, bitline들과 V1, V2의 연결이 끊어지게 되면서 read전 standby value로 돌아가게 된다. 이는 read되는 동안 SRAM cell을 덜 stable하게 만든다. reading으로 인해 memory bit이 fipped되면 안된다. read 불안정성 문제에 대해서는 나중에 논의하겠다.

2) Write 동작

Write logical '0'-> logical '1'

① 두 bitline들을 Vdd로 precharge시킨다. 단, 낮은 임피던스의 Z로 연결되어 있다.

② WL : High(selected) -> access transistor : ON

③ t(WE,write enable) 이후엔, "write enable" 신호가 주어지면서 V(BLT) = 0, V(BLC) = Vdd 이 된다.

④ V(BLT)가 V1을 0으로 만들고, V(BLC)가 V2를 Vdd로 만든다.(Write logical '1')

⑤ WL : Low -> access transistor : OFF

Write logical '1'-> logical '0'

반대의 과정이다.

1.2 CMOS SRAM Cell의 Device Sizing

CMOS SRAM Cell을 줄일수록 좋다. 하지만 read stability 와 write instability의 관점에서 디바이스는 일정량의 적절한 on conductance(strength)를 가져야할 것이다.

아까 Read에서 Q6에서 Q2로 전하가 흘러 V(BLC)와 V2가 변한다고 언급한 적이 있었다. stability를 높이기 위해서는 V(BLC)가 내려가더라도 V2는 변하지 않도록 해야한다. 그러기 위해서 Q2의 on resistance를 Q6보다 훨씬 작게 만든다. 그러면 V2에 인가되는 전압이 굉장히 작아질 것이다. Q1, Q5도 마찬가지다. 따라서 정리하면,

R(Q2) < R(Q6) (이를 Q2가 Q6보다 stronger(wider) 하다고 말한다.),

R(Q1) < R(Q5) (이를 Q1이 Q5보다 stronger(wider) 하다고 말한다.) 를 만족해야 한다.

Write에서도 마찬가지다.

전류가 Q3에서 Q5로 흐르고 있고, V1을 V(BLT)에 가깝게 만들고 싶기 때문에

R(Q5) < R(Q3) (Q5이 Q3보다 stronger해야한다.)

R(Q6) < R(Q4) (Q6이 Q4보다 stronger해야한다.) 를 만족해야 한다.

정리하면 다음과 같다.

<Requirements for read operation>

R(Q2) < R(Q6)

R(Q1) < R(Q5)

<Requirements for write operation>

R(Q5) < R(Q3)

R(Q6) < R(Q4)

이 요구조건을 충족할 수 있는가?

unstrained silicon을 사용하는 CMOS에서 Q3,Q4를 가장 약한 트랜지스터로 만드는 것은 굉장히 쉽다. 그 이유는 두 트랜지스터가 pMOSFET이기 때문에 nMOSFET보다 mobility가 절반이기 때문이다. 따라서, 같은 device channel length에 같은 Vt를 가지고 있다면, pMOSFET에 흐르는 전류는 절반이 될 것이다. 즉, Q3,Q4를 minimum size의 pMOSFET으로 Q5,Q6를 minimum size의 nMOSFET으로 둔다면, write operation 요구조건은 충족할 수 있게된다.

read operation을 충족하기 위해서는 Q1,Q2가 minimum 사이즈보다 더 커야한다. Q1,Q2의 width를 Q5,Q6보다 2배로 키운다면 read operation 요구조건도 충족할 수 있다.

strained silicon을 사용하는 CMOS에서는 pMOSFET과 nMOSFET의 mobility가 다르게 증가하기 때문에, Q3,Q4를 가장 약한 tansistors로 만들기 위해 신경을 써야한다.

1.3 Static Noise Margin of a CMOS SRAM Cell

메모리 셀의 안정성은 static noise margin(SNM)으로 특징지어진다. 노이즈 전압의 magnitude에 따라 memory bit의 flip이 일어날 수도 있기 때문이다. standby상태에서는 cell과 bitlines들이 끊어져 있지만, read or write operation에서 cell과 bitlines은 coupling되어 있다. 따라서 CMOS SRAM의 노이즈마진은 standby 상태, read operation 상태, 그리고 write operation 상태에서 논의될 것이다.

SNM in standby mode

standby mode에서는, access tansistors는 OFF된다.

먼저, cell이 logical "0" state일 때, cell은 점 A에 위치해있고, V2 = 0, V1 =Vdd이다. cell flip 시킬 수 있는 noise voltage of magnitude Vn이 있다고 가정하자. 예를 들어 인버터 1에 +Vn이 더해지고, 인버터 2에 -Vn이 더해진다고 가정하자. 그러면 아래 그림과 같은 결과가 일어날 것이다. 일단 노이즈가 더해지기 전에, nMOSFET이 pMOSFET보다 전류가 stronger하기 때문에, transfer curve는 symmetric 하지 않다. 만약 노이즈가 더해지게 되면 인버터 1의 transfer curve는 수평하게 왼쪽으로 이동하고, 인버터 2의 transfer curve는 수직하게 위쪽으로 이동한다. 그렇게 교차점 A가 없어지고 교차점 B만 남게 되면 cell의 state는 logical "0"에서 logical "1"로 바뀌고, 이때의 minimum 노이즈 전압을 SNM이라 부른다. 그래서 그래프에서 살펴보게 되면, 두 transfer curve 내부에 갇히는 maximum square의 side로 SNM이 측정된다고 볼 수 있다. cell이 logical "1" state일 때도 비슷한 방법으로 구할 수 있다.

SNM during read access

reading 중에는 output node가 ON된 access transistor를 통해 Vdd 전압이 걸린 bitline에 연결되어 있기 때문에 high-to-low transition이 덜 가파르고, input high(Vdd)에서의 output voltage가 zero으로 가지 않게 된다. 실제로, CMOS SRAM cell은 작아진 노이즈 마진 때문에 read operation 동안에 노이즈로부터 취약하게 된다.

SNM during write access

state '0'에서 state '1'로 write 할때 V(BLT) = 0, V(BLC) = Vdd 가 access transistor에 인가된다. state '0'에서 state '1' 로 flip된다는 의미는 (V1, V2)가 (Vdd, 0)에서 (0, Vdd)로 바뀐다는 것을 의미한다. 근데 V(BLT)에 이미 0이 인가되어 있고, write operation requirements에서 R(Q5) < R(Q3) 이므로 Vout1이 상당히 감소하게 된다. 따라서 위 그림 (c)처럼 transfer curve가 형성되게 된다. 따라서 state '0'에서서의 noise margin이 완전히 사라지게 된다.

1.4 Scaling Issues of CMOS SRAM Cells

Gate length가 scaling down됨에 따라 Vdd와 Vt가 같이 작아지게 되는데, 이때 overdrive ratio인 Vdd/Vt도 같이 작아지는 경향성을 띄게 된다. 이 말은 transfer curves와 I-V characteristics이 Vt variation에 더 민감해진다는 것을 의미한다. CMOS SRAM의 SNM은 디바이스 자체의 영향을 받을 뿐만 아니라 SRAM array에는 굉장히 많은 개수의 cell들이 있어, 각 device parameter들은 통계적인 분포를 가진다.

예를 들어, scaling issues들은 다음과 같은 factor의 영향을 받는다.

1. Vt variation due to short-channel effect

short channel effect로 인해 일단 Vt가 roll-off 된다. 또한, 공정에 의한 tox나 doping concentration variation도 Vt에 영향을 미친다. 이런 요소들은 device mismatch 혹은 SNM의 감소를 발생시킨다. gate length mismatch는 symmetrical한 방법으로 셀을 설계함으로써 최소화 시킬 수 있다.

2. Vt variation due to statistical dopant fluctuation

이전 챕터에서 언급한 것처럼 작은 MOSFET에 존재하는 도펀트 원자들 개수가 달라짐에 따라 Vt가 영향을 받는다. 100nm정도의 최소 너비를 가지는 CMOS SRAM devices에 대해 standard deviation of Vt fluctuation은 대략 30mV정도이다. 이 dopant fluctuation에 의해 발생하는 Vt variation은 트랜지스터를 재배치하는 것으로 최소화시킬 수 없기 때문에, 치명적이며 심할 때는 SNM들 중 하나를 완전히 없앨수도 있다.

3. Vt variation due to high-field effect

high-field effect에 의해 degradation이 일어나면, 그 결과로 Vt가 증가하게 된다. 따라서 device pair가 공정 과정에서 잘 matched 됐다고 하더라도, 그 특성은 burn-in stress과 operation 과정에서 mismatched로 바뀔 수 있다. 최근 CMOS 세대에서는 negative-bias-temperature instability(NBTI)에 의해 pMOSFETs의 Vt instability가 가장 큰 걱정이라고 한다.

'전공글 > 이론정리' 카테고리의 다른 글

| Steep Slope Devices (0) | 2023.03.08 |

|---|---|

| [이론정리] Memory Devices ③ : Nonvolatile Memory (0) | 2023.02.09 |

| [이론정리] Memory Devices ② : DRAM (0) | 2023.02.07 |

| [이론정리] Memory Devices : Introduction (0) | 2023.02.03 |

| [현대반도체소자공학] SRAM과 DRAM, 그리고 Nonvolatile memory (0) | 2023.02.02 |