[현대반도체소자공학] SRAM과 DRAM, 그리고 Nonvolatile memory

본 내용은 <현대 반도체 소자 공학, Chenming Calvin Hu 저>을 참고하여 제작되었다.

메모리 소자들은 휘발성 메모리인 SRAM(static RAM), DRAM(dynamic RAM)과 가장 일반적으로 사용되는 비휘발성 메모리인 flash memory 등 크게 세 가지로 나눌 수 있다. 세 종류의 메모리가 공존하는 이유는 각각의 메모리가 그 고유의 장점과 한계를 가지기 때문이다. 아래의 표를 참고하자.

새 데이터들을 추출하기 위해서 판독 헤더와 디스크를 움직이는 데 상당한 지연시간이 있는 하드디스크와 달리 RAM(random access memory)은 모든 데이터 바이트들이 언제든지 접근이 가능하다.

SRAM은 기본적인 CMOS 기술과 같은 트랜지스터와 제조 공정만을 필요로 한다. 그러므로 집적을 하거나 CMOS 회로에 내장하는 것이 가장 쉽다. DRAM셀은 SRAM셀과 다르게 몇 가지 특별한 공정 단계를 필요로 한다. 플래시 메모리 셀은 비휘발성의 저장을 수행하기 위해 다양한 물리적인 메커니즘 중 하나를 사용한다. SRAM>DRAM>플래시 메모리 순으로 크기가 크며, 플래시 메모리는 그 자체의 느린 쓰기 속도와 제한된 쓰기 사이클이라는 크나큰 단점이 존재한다. 하지만, 경제적이며 소형이기 때문에 휴대용 장치에 많이 사용된다.

1. SRAM

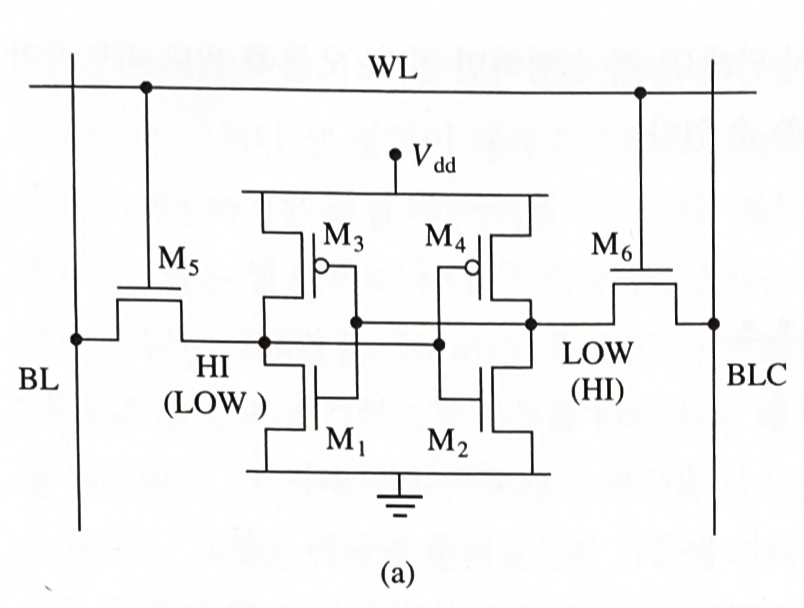

기본적인 SRAM 셀은 한 비트의 데이터를 저장하기 위해서 6개의 트랜지스터를 사용한다. 그림 (a)와 같이 그 코어는 2개의 교차 결합된 인버터들로 구성된다. 왼쪽 인버터의 출력이 오른쪽 인버터의 입력에 위치해 있고, 오른쪽 인버터의 출력이 왼쪽 인버터의 입력에 위치해 있다. 따라서, 왼쪽 인버터 출력이 high 상태이면 오른쪽 인버터 출력이 low가 되고, 이 오른쪽 인버터 출력이 다시 왼쪽 인버터 출력을 high로 만든다. 이 양성피드백은 이러한 상태가 저장되고 안정적이게 해준다. 왼쪽 인버터 출력이 low 상태일때도 마찬가지다. 따라서 이 셀은 "0"과 "1"로 나타낼 수 있는 두 가지 상태를 가지며, 한 비트의 데이터를 저장할 수 있다. 많은 동일한 SRAM 셀들은 XY 배열로 정렬되어 있고, 각 셀들의 횡은 워드라인(WL), 각 셀들의 열은 비트라인쌍(BL 및 BLC)에 연결되어 있다.

그림을 살펴보면 M1, M2, M3, M4는 두 개의 인버터를 형성하는 데 쓰인다는 것을 알 수 있다. 그러면 M5, M6는 어디에 쓰이는 것일까? M5, M6는 패스 트랜지스터라고도 불리며, 인버터의 출력을 비트라인에 연결한다. 저장된 데이터를 읽기 위해서는 선택된 셀의 WL 전압이 상승하여 패스 트랜지스터들을 켜준다. 그런 뒤, 감지 증폭기(sense amplifier)를 통해 BL과 BLC의 전압을 비교하여 저장된 상태를 결정한다. 셀에 왼쪽 low 상태를 쓰기 위해서는, 예를 들면 BL을 low 상태로 설정하고 BLC를 high 상태로 설정한다. 그 다음, 워드라인 전압이 상승하면 인버터들은 이 새로운 상태로 강제로 바뀌게 된다.

SRAM 셀은 모든 메모리 중에 가장 빨리 동작되도록 한다. 하지만, 6개의 트랜지스터를 필요로 하기 때문에 원가가 가장 높다. SRAM 셀들은 종종 속도가 중요한 연산 장치에 내장되어 캐시 메모리로 사용된다.

2. DRAM

DRMA 셀은 그림과 같이 오직 한 개의 트랜지스터와 한 개의 커패시터를 포함한다. 그러므로 단위 면적당 비트 수 가 크며 비트당 원가는 낮다. 그림을 보면 셀 커패시터의 한쪽 끝은 접지되어 있다. "1"과 "0" 상태는 셀 커패시터를 Vdd 또는 0으로 충전시키는 것을 나타낸다. 좌측 상단 셀에 데이터를 쓰기 위해서는 WL 1을 높은 전압으로 올려서 트랜지스터를 켜주고(커패시터를 비트라인 1에 연결시키고), 비트라인 1에 "1" 을 쓰기 위해 Vdd를 설정하거나 "0" 을 쓰기 위해 0V를 설정하면 된다. 오른쪽 셀도 비트라인 2에 적절한 값(Vdd 또는 0)을 설정해서 동시에 쓸 수 있다. 밑의 셀도 비트라인 2에 적절한 값(Vdd 또는 0)을 설정해서 동시에 쓸 수 있다.

각 비트라인은 고유한(unevitable) 커패시턴스인 Cbit line을 가진다. 좌측 상단의 셀로부터 저장된 테이터를 읽기 위해서는 비트라인 1을 Vdd/2로 예비충전시킨 다음 부동(floating) 상태로 두고 WL 1 전압을 올려서 셀 커패시터를 더 큰 Cbit line과 병렬 연결시킨다. 셀 커패시터의 전압(Vdd or 0)에 따라 셀 커패시터는 비트라인의 전압을 C*Vdd/2(C+Cbit line)만큼 올리거나 내려주는데 이전압은 대개 수십 밀리볼트 정도이다. 비트라인에 연결된 감지 증폭기가 저장된 데이터를 결정하기 위해 이 전압의 변화를 감시한다. 하나의 WL에 연결된 모든 셀들은 동시에 읽힌다. 각 읽기 동작 후에는 읽기 동작에 의해 커패시터의 전하가 파괴되므로 동일한 데이터가 자동적으로 셀에 다시 쓰인다(rewrite).

DRAM 커패시터는 제한된 시간 동안만 데이터를 유지할 수 있는다. 그 이유는 전하가 커패시터 유전물질, PN 접합(트랜지스터 S/D), 트랜지스터의 문턱전압 이하 누설 전류에 의해 지속적으로 누설되기 때문이다. 데이터의 손실을 막기 위해서는 1초에 여러 번 리프레시(refresh)가 되어야 한다. 리프레시는 대기 전력을 소모하므로, 전력소모를 최소화하기 위해 더 많은 전하를 저장할 수 있도록 셀 커패시터를 크게 하여 리프레시 간격을 증가시켜야 한다. 큰 셀 정전용량은 또한 빠르고 밑을 만한 큰 읽기 신호를 만드는 데 중요하다. 이는 셀 영역이 감소되는 현 기술발전의 경향성과는 반대이다. 따라서 엔지니어들은 매우 얇은 커패시터 유전물질을 적용하는 것 외에, 엔지니어들은 셀 면적보다 더 큰 커패시터 면적을 제공하기 위해 복잡한 3차원 구조를 강구해 왔다.

그 복잡한 3차원 구조의 예시로 그림 (a)와 그림 (b)가 소개되어 있다.(그림 (a)는 컵 모양의 커패시터를 포함한 개략도, 그림 (b)는 DRAM 셀 단면 전자현미경 사진을 나타낸다.) 각 커패시터는 두 개의 전극을 가지는데, 한쪽 전극은 컵 모양으로, 폴리실리콘 혹은 금속이다. 그것은 바닥에 폴리실리콘 기둥에 의해 하부 트랜지스터에 연결되어 있다. 다른 전극 또한 폴리실리콘으로 만들어지며, 그 전극은 나머지 공간을 채우고 있다. 얇은 유전 필름이 두 전극을 나눈다.

허나 훨씬 단순한 DRAM 공정 기술은 셀 면적을 상당히 희생하지만 논리 CMOS 기술에 집적될 수 있다. 이러한 내장 DRAM 기술은 필요한 비트 수가 큰 경우 내장 SRAM의 매력적인 대안책이 될 수 있다.

3. 비휘발성 (플래시) 메모리

SRAM과 DRAM은 전원에 연결되지 않으면 저장된 내용을 잃어버리는 것과 반대로 비휘발성 메모리(nonvolatile memory, NVM)는 전원 공급 없이도 많은 해 동안 그 내용을 저장할 수 있으며, 휴대전화나 대부분의 연산장치에 기반을 둔 시스템에서 프로그램 코드 저장장치(code storage)로 사용된다. 또한 비휘발성 메모리는 크기가 작고, 전력 소모가 적으며, 움직이는 부분이 없기 때문에 문서, 사진, 음악 그리고 영화를 저장하는 하드디스크나 CD를 뛰어넘는 데이터 저장 미디어로 선호되고 있다. 많은 형태의 비휘발성 메모리 소자가 있으나, 널리 사용되는 형태만 설명하도록 하겠다.

이 구조는 MOSFET에서 한 가지를 변경하여 얻을 수 있다. 바로 게이트 절연막을 그 사이에 전하-저장층이 끼워진 두 절연막으로 교체하는 것이다. 전하-저장층은 실리콘 질화막이나 다른 고농도의 전자트랩을 가진 절연막이 될 수 있다. 전자가 절연막에 트랩되면 트랜지스터는 높은 Vt를 가진다. 낮은 Vt와 높은 Vt 상태는 각각 "0" 과 "1" 상태를 나타내고, Vt를 확인하는 감지 회로로 쉽게 읽힐 수 있다. 전하-저장층은 도체일 수도 있으나, 실제로 가장 중요하고 널리 사용되는 물질은 폴리실리콘이다. 비휘발성 메모리는 플로팅 게이트 메모리(floating-gate memory)라고도 불린다. 그 이유는 폴리실리콘 층이 전기적으로 플로팅 상태인 트랜지스터의 게이트이기 때문이다. 그림 (c)는 전자를 전하-저장층에 어떻게 주입하는지를 보여준다. 이는 즉 "1"을 쓰는 방법이다. 약 20V를 게이트에 가해주면 높은 전기장이 형성돼 전자들을 반전층에서 전하-저장층으로 터널링시켜준다. 반대로 (d)처럼 substrate에 20V를 가해주면 저장된 전자들이 기판으로 터널링하여 셀이 "0"으로 소거 된다.

이 터널링에 의한 소거 동작 속도는 느리므로(ms초 정도 소요, SRAM이나 DRAM은 ns) 이러한 비휘발성 메모리는 바이트 단위보다는 킬로바이트 단위의 소거를 한다. 큰 메모리 블록 단위의 전기적인 소거를 플래시 소거(flash erase)라 하고, 이러한 형태의 메모리를 플래시 메모리(flash-memory)라고 한다. 플래시 메모리는 비휘발성 메모리(NVM)의 유명한 제품 종류이므로 두 용어가 종종 혼용된다. 터널링에 의한 쓰기 또한 매우 느려서 동시에 수백 바이트씩 수행된다.

또 다른 방식으로 셀에 테이터를 쓰는 방법을 (e)에 나타내었는데, 소오스가 접지되어 있고 게이트와 드레인에 정상적인 전압보다 높은 전압을 걸어주면, 드레인 근처의 핀치오프(또는 속도 포화) 영역에 높은 전기장이 생긴다. 이 영역을 지나가는 전자들의 일부가 절연막 에너지 벽을 넘어 전하-저장층으로 갈 수 있는 충분한 에너지를 얻게 된다. 이러한 방법은 터널링보다 더 빠르지만 더 많은 전류와 전력이 들어간다. 이렇게 에너지가 큰 전자들을 고온 전자(hot electron)라고 하고, 이러한 쓰기 방법을 고온 캐리어 주입(hot carrier injection), 또는 간단히 HCI라고 한다.

또 다른 기술에서는 위 그림처럼 저항이 극히 얇은 금속 이온의 필라멘트로 되어 있다. 이 필라멘트는 전기 펄스에 의해 몇 개의 금속 이온을 움직임으로써 부서져서 Rhigh 상태가 된다. 이것은 바대 극성의 전기 펄스에 의해 복귀된다. 이러한 메모리 개념을 금속 마이그레이션 메모리(metal migration memory)라 한다.